Ring Counter and Johnson Counter explained

Last Updated on September 12, 2021 by Engr. Shahzada Fahad

Table of Contents

Ring counter:

A ring counter is typical application of the shift register. In ring counter we store one bit in flip flop and it will rotate in the whole system. We will use D flip flop for its construction. In ring counter the output of the last flip flop is connected with the input of first flip flop. If we compare the ring counter with the shift register there is only one change. Q3 which is the output of the last flip flop is connected to the input of the first flip which isD0 But in case of shift register we do not have any feedback like this but we have only Q3 as an output and this is the only change we will find in the ring counter. The number of states in general when we have four bit counter we use four flip flops. Suppose we have 4 bit ring counter and we have use four flip flops and to find the number of states we will find it by using the formula:

24 = 16

From the above we know that we have 16 states and it will count from 0 to 15 but it is when we have normal counter but this is special type of counter in which we cannot find the states like this. In case of ring counter the number of states is equal to the number of flip flops used.

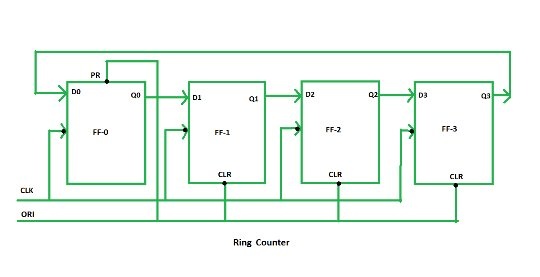

Ring Counter Circuit diagram:

The output Q0 of the first flip flop will be given to the input D1 of the second flip flop, the output Q1 of the second flip flop will be given to the input D2 of the third flip and output Q2 of the third flip flop will be given to the input of the fourth flip flop and the output Q3 of the fourth flip flop will be given to the input of the first flip flop. The clock is given to all the four flip flops simultaneously at the same time that is why it is synchronous counter and also we have use the overriding inputs. Now we will store one bit in flip and with the clock its position will be change. The ORI is a signal that is given to the overriding inputs of the flip flops.

The pre-set and clear are active low inputs. If we want to set 1 in a flip flop we then we will apply zero to that flip flop because it is active low input. When the pre-set is zero then the output of the flip Q is equal to 1. If we want the flip flop output to be zero we will activate clear input of that flip flop. Clear and pre-set which are asynchronous inputs when these are activated, the input will not affect the output due to which these inputs are called overriding inputs. So when the clear and pre-set value are equal to 0 the output of the flip flop output will be 0 and when the pre- set is equal to 1 and clear is equal to 0 then the flip flop out will be 1.

It will set the flip flop and when clear is equal to 0. The Q will equal to zero and it does not look for the value of the clock or D the input. They are going to override the output so we have used the pre-set and clear input in a certain manner that when the ORI signal will be low the pre-set and clear will be in action. In the circuit we can see that the ORI is connected to the clear of all flip flops except the first flip flop with which it is connected with its pre-set. We will not connect the clear of the first flip flop.

When the ORI signal is given low and no clock signal is applied to it. It will make the output Q1 equal to zero because clear is low and in the same way Q2 and Q3 will also be 0. When the pre-set is low the output of the first flip flop will be high so Q0 will be 1 and it will follow a circular path to form a ring.

When ORI will be high so that the clear and pre-set will not affect the output throughout the operation ORI will be high. Now the clear and pre-set are set to be 1. Now we will move to the clock as all the four flips are negative edge trigger so there will be change in the circuit or the D flip flop whenever we have a falling edge.

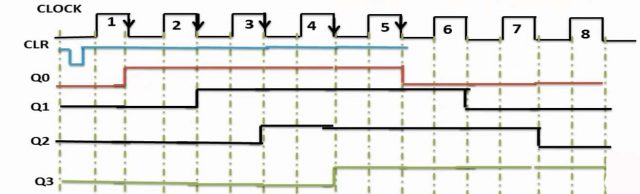

For the first falling edge we can see that the output zero of the last flip flop will be acting as input to the first flip flop. In the same way D1 will be equal to 1 because Q0 is equal to 1 and they are connected as D1 is 1 then the Q1 will also be 1. D2 and D3 are equal to zero due to which the Q2 and Q3 will also be equal to zero.

Now for the second falling edge now again the input at the D0 is zero Q0 is zero and D1 will be zero as Q1 was 1 due to which D2 will be 1 so the Q2 will also be 1. D3 and Q3 will be zero.

Now for the third falling edge now again the input at the D0 will be zero Q0 will be 0 and D1 will be 0, Q1 will 0 due to which D2 will be 0, D3 will be 1 as Q2 was 1 due to which Q3 will also be 1.

For the next falling edge D0 will be 1 because the output Q3 is connected with D0 and again the whole process will be restart.

| Clear/ Pre-set | Clock | Q0 | Q1 | Q2 | Q3 |

| 0 | No clock | 1 | 0 | 0 | 0 |

| 1 | ↓ | 0 | 1 | 0 | 0 |

| 1 | ↓ | 0 | 0 | 1 | 0 |

| 1 | ↓ | 0 | 0 | 0 | 1 |

| 1 | ↓ | 1 | 0 | 0 | 0 |

As we see that 1 is rotating so therefore it is known as ring counter. The waveform of the ring counter is shown below.

Johnson Counter:

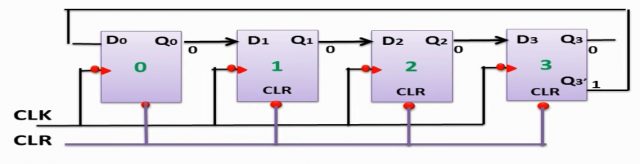

The Johnson counter is also known as twisted tail ring counter. In the ring counter we given the output of the last flip flop into the input of the first flip but in the Johnson counter the last flip flop complemented output is given to the input of the first flip flop. In this counter negative edge flip flop are used. In Johnson counter the number of states is equal to twice the number of flip flops.

So if we use 4 flip flops we will have 8 states so the number of the states are double. We applied clock simultaneously to all flip flops. The clear input is applied to all the flip flops. The output of the first flip flop which is Q0 is given at the input of the second flip flop D1 and the output of the second flip flop which is Q2 is given to input of the third flip flop which is D2 and the complemented output (Q3) ̅

will be given to the input of the first flip D0. The difference between the ring counter and Johnson counter is that it does not require pre-set.

Working of Johnson Counter:

When the clear is zero and no clock is applied all the output will be zero because we know that clear and pre-set are active low inputs so as the clear is zero due which all the outputs are zero. As the Q3 is zero (Q3) ̅ will be 1 and feedback to the first flip flop input D0. When the clear is equal to 1 and then we see the first falling edge of the clock the output Q0 will be 1 and the remaining inputs and outputs of the flip flops will be zero. When the second falling edge of the clock occurs as the input D0 is 1 the output Q0 will be 1 as it is connected with the D1 so the Q1 will also be 1 and the remaining flip flop inputs and outputs will be zero. When the third falling edge of the clock will occurs again the input D0 is 1 the output Q0 will be 1 similarly D1 and Q1 will also be 1 as it is connected with the D2 so D2 and Q2 will also be 1. D3 and Q3 will be 0. When the fourth falling edge of the clock will occur all the input and output of the flip flops will be 1. When the Q3 will be 1 (Q3) ̅ will be equal to 0 and the input to the D0 will be zero. Due to which the output Q0 will be zero and the remaining outputs will be 1. The same process will be continue for the remaining inputs and outputs.

| Clear/ Pre-set | Clock | Q0 | Q1 | Q2 | Q3 |

| 0 | No clock | 0 | 0 | 0 | 0 |

| 1 | ↓ | 1 | 0 | 0 | 0 |

| 1 | ↓ | 1 | 1 | 0 | 0 |

| 1 | ↓ | 1 | 1 | 1 | 0 |

| 1 | ↓ | 1 | 1 | 1 | 1 |

| 1 | ↓ | 0 | 1 | 1 | 1 |

| 1 | ↓ | 0 | 0 | 1 | 1 |

| 1 | ↓ | 0 | 0 | 0 | 1 |

| 1 | ↓ | 0 | 0 | 0 | 0 |

Clock signal:

Clock signal is a timing signal and is to provide sequence to the circuit. it is rectangular signal which we also call clock pulse with duty cycle equal to 50%. The upper part is known as high signal and the lower part is known as low signal. It is basically train of pulses and the part from low to high is known as leading edge and the part of clock from high to low is known as trailing edge. The combination of the high and low is known as one cycle is represented with T and is the time period. Clock signal is used for the combinational circuit.

The output of the above sequential circuit will depend on the present input as well as its previous output so the output state of the combinational circuit will be stored in the memory and when we will provide the feedback to the combinational circuit it will be decided by the clock. We will get the output when we apply the clock pulse. The clock pulse will work like control input to the memory. The one output of the combinational circuit is given to the memory where it store. So there are different types of process in the sequential circuit and these processes are not randomly operated. In order to operate it in sequence we will need a timing signal so will apply a clock signal that will provide a sequence to the circuit. The clock signal will synchronize all the process. In flip flop clock signal decide whether the output will be change or not. We can decide the speed of the circuit with the help of clock signal by varying its clock frequency.

Clock frequency = 1/T

The ratio of time for which signal is high to the total time is called duty cycle. When the low state time and high state time which means that its duty cycle is 50%.

Triggered methods:

There are two types of triggered method which are:

- Level triggering

- Edge triggering

Level triggering:

Level triggering have further two types which are:

- Positive level triggering

- Negative level triggering

The flip flop which will operate on the positive level of the clock are known as positive triggering flip flops and the flip flops which operate when the negative level of the clock occurs are known as negative level triggering.

Edge triggering:

Similarly edge triggering are also of two types:

- Positive edge triggering

- Negative edge triggering

In positive edge triggering the flip will operate on the positive edge of the clock which will be from 0 to 1 and in negative edge triggering the flip flop will operate on the negative or the falling edge of the clock which will be from 1 to 0.

Discover more from Electronic Clinic

Subscribe to get the latest posts sent to your email.

Here we go