Counters in Digital Electronics: Synchronous, Asynchronous and Ripple Counter

Last Updated on December 2, 2022 by Engr. Shahzada Fahad

Table of Contents

Counters in Digital Electronics:

As the name implies, counter is a type of circuit, which counts or which can be used for counting purposes. Or counting is such a digital device, which counts clock pulses (which are received from clock) in binary (actually, counter is a specific type of a register, which is designed in order to count number of pulses being received on its inputs). In other words, such sequential logic circuits composed via connecting or wiring together flip-flops, which are used to count binary pulses being applied (provided) on these flip-flops, are called counters. When a clock pulses are applied on input of some counter, the flip-flops present inside the counter change its state in such a way that stored binary number on it reveals the number of input pulses passing through it (i.e. it can be ascertained by looking at a flip-flop’s output that how many clock pulses have been applied on its input).

The basic function of a counter is to record the number of occurrences of an input. In computers and other digital systems, counting is imminently essential for recording the number of events during a specific point of time (count pulses received regularly from a normal waveform, are called events). Therefore, in order to count number of pulses being received on input line during a specific time period or in order to count the number of occurrences of an event, counters are used. Counters are really handy in time sequences for the control of operations in a digital system. Remember, that as a counter has to memorize its previous state, therefore it also has a memory feature and they are manufactured with help of flip-flops.

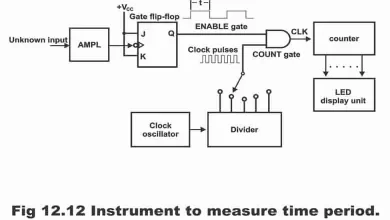

Counters are heart of every digital system, because they are massively used in nearly all designed digital and computerized systems (i.e. a counter is probably the most widely and most versatile sort of device being used in digital systems). As a clock driven counter is used to count the number of clock pulses and as clock pulses always occur during known intervals or specific intervals, therefore counters are used as time measurement instruments (e.g. clocks), period or frequency measurement instruments, speed and distance measurement instruments, addressing, frequency dividing and as a memory unit.

Synchronous counters

Synchronous counters are such counters in which clocks of all flip-flops are inter- shorted together (because we know that counters are made by means of combining flip-flops together and flip-flops operate via clock provided on its input). In other words, counters are clocked (i.e. connected with clock or pulse provided from the clock) in such a manner that all flip-flops being present on the counter, are triggered together simultaneously (i.e. every flip-flop present on the synchronous counter receives an equivalent or same clock pulse). Where ever propagation time delay or a high speed is desired, synchronous counters are preferred.

Asynchronous counters

Asynchronous counters are such counters in which all present flip-flops cannot trigger together simultaneously. In other words, counters in which flip-flops clocks are not shorted together, are called asynchronous counters. In these counters, first of all flip-flop is connected with the clock (i.e. first clock pulses are provided on flip-flop or clock is provided first to a flip-flop) whereas clock of the next flip-flop is connected with the output of previous flip-flop. This point can also be described as such that clock of second flip-flop depends on output of the first flip-flop. As the propagation delay time (time required for a change in a gates’ output with respect to a change in a gates’ input, is called propagation delay time. In simple words, the operational speed of logic circuit is known as its propagation) of asynchronous counters is high, therefore speed of asynchronous counters is low as compared to synchronous counters. Remember that ripple counter is an asynchronous counter and an asynchronous counter is also known as a serial counter.

Ripple Counter

An asynchronous counter, in which every flip-flop triggers by means of output of previous flip-flop, is called a ripple counter or ripple-binary counter. In other words, a counter in which output of one flip-flop is used as a clock input for the next flip-flop, is known as ripple counter. In simple words, counter comprising flip-flops arranged in a cascaded series, is called ripple counter (it has to be remembered here that if output of one flip-flop is considered input for other flip-flop, then this method of connecting multiple flip-flops in a serial fashion is called cascade). The greatest advantage of a ripple counter is that it is simple, however its speed is low. It can however, also be used as a frequency divider.

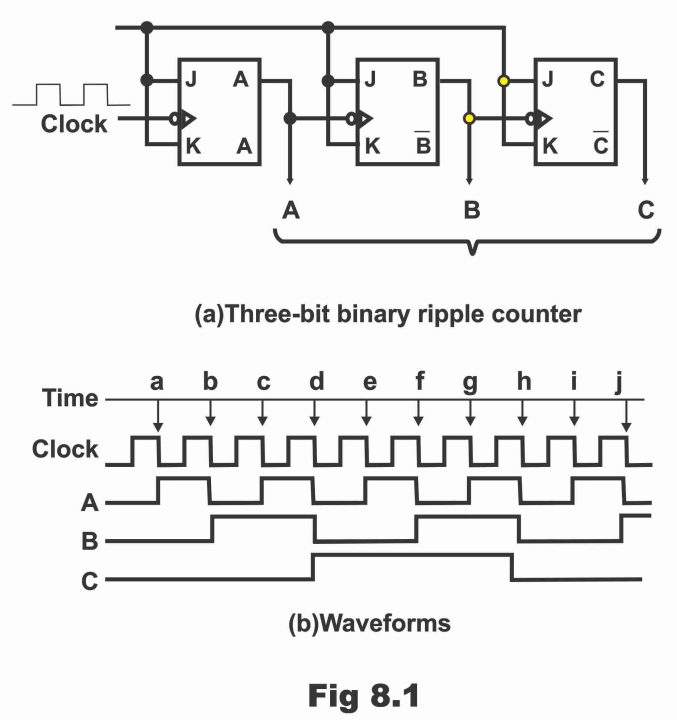

A binary ripple counter is fabricated by means of using clocked JK flip-flops. In figure 8.1 (a), a 3 – bit binary ripple counter constructed by means of combining three negative edge-triggered JK flip-flops in a cascade, has been illustrated. According to this figure, normal output of one flip-flop has been given a toggle or clock input of other flip-flop. System clock provides a square wave, which drives flip-flop A. A ‘s output drives B and B’s output drives flip-flop C. All J and K inputs have been connected with +VCC (i.e. JK inputs of every flip-flop is high). It means that every flip-flop toggles (i.e. changes its state) only when negative transition (NT) is provided on its clock input. The input pulses, counting of which has been desired, are always provided on toggle input (i.e. clock input) of the first flip-flop. This has been illustrated via following figure.

Figure 8.1

In order to understand operation of this type of counter, it has to be inculcated in mind that a JK flip-flop changes its state every time only when trailing edge of clock pulse is received on its clock input (i.e. every flip-flop is negative edge-triggered). Next flip-flop changes its state only when normal output of the previous flip-flop changes from set to reset (i.e. it turns binary 1 from binary 0). In other words, prior to triggering B flip-flop, A flip-flop has to change its state. similarly, B flip-flop should also change its state prior to triggering of C flip-flop. Triggers in a flip-flop move just like a ripple in water, therefore total propagation delay time equals to the sum of individual delay time being occurred in every flip-flop. For example, if the delay time of every flip-flop in this 3-flip-flops counter is 10ns, the total propagation delay time of the counter will be 30ns, which points or hints towards a low speed of this counter.

Operation

The waveform shown in the figure 8.1 (b), represents the operational mechanism of this counter. Suppose that all flip-flops are reset initially (i.e. their output is zero). If we consider A as the smallest bit or LSB (least significant bit) and C as the largest bit or MSB (most significant bit), then counters’ output in the initial state of the counter will be as follows;

CBA = 0 0 0

Every time, when negative clock transition is received, (which has been reflected via a downward tilted small arrow (↓) sign on the time line in figure “b”) then flip-flop A changes its state. Therefore, flip-flop A tends to be high at point “a” on the time line and it turns low on next negative transition (i.e. point b) as has been illustrated vide A waveform in figure (b). if we carefully study this particular waveform, it becomes evident that waveform frequency formed on flip-flop A ‘s output, is half as compared to clock frequency.

As A flip-flop operates for B flip-flop as a clock, therefore every time when A flip-flops’ waveform is low, flip-flop B toggles (i.e. it changes its state). Thus, B flip-flop located at point “b” on time line turns high, as can be seen from B waveform as shown in figure (b). This flip-flop tends to get low on point d and becomes high on point once again by means of toggling. It is absolutely clear from flip-flop B’s output waveform that its frequency is one-half of flip-flop A’s frequency and one-fourth (1/4) of clock frequency.

Similarly, B flip-flop also serves as a clock for C flip-flop. Therefore, every time when B flip-flop’s wave form is low, flip-flop C toggles. Thus, flip-flop C becomes high at point “d” of the time line and turns low again at point “h”. As has been illustrated via C wave form in the figure (b). As such, C wave form’s frequency becomes one-half relative to B wave form’s frequency, but one-eighth as compared to clock frequency.

It has become clear from the afore-mentioned discussion that, flip-flops output state represents such a binary number which is equal to the number of NTs (i.e. clock pulses) transmitted through the counter. Thus, output state on time line prior to point “a” is CBA = 0 0 0. At point “a” of the time line output state changes and becomes CBA = 0 0 1 and at point “b” it changes and becomes CBA = 0 1 0. And as this process moves on. If the wave form given in figure is meticulously studied, we get to know that with every negative clock transition, counter’s counting process increases. This has been elaborated via a truth table shown in figure ©. As this counter is a 3-bit binary counter (because three flip-flops have been cascaded into it) therefore, this counter can be used for counting a maximum of seven clock transitions.

Counter starts with 000 count, and by means of addition of every one count per clock transition, it reaches 111 count. After reaching 111 count, counter resets and returns back on 000 and count cycle re-starts again. Therefore, we may say that this ripple counter functions only in the count- up mode.

As a binary ripple counter counts in a straight binary sequence, therefore it is quite simple to understand that there are “2” output states of a counter consisting of “n” flip-flops. For example, a counter having 3 flip-flops have 23 = 8 output states (i.e. 000 to 111). Likewise, a counter containing four flip-flops, has 24 = 16 output states (i.e. from 0000 to 1111) and a counter comprising five flip-flops, has 25 = 32 output states (i.e. from 00000 to 11111). However, the highest binary number, which can be denoted by means of “n” flip-flops arranged in a cascaded series, is equivalent to 2n -1 decimal numbers. For example, a counter with three flip-flops can count maximum up to 7 decimal numbers (i.e. 23-1 = 7). A counter comprising four flip-flops can count maximum up to 15 decimal numbers (i.e. 24-1 = 15). Remember that as a three flip-flop counter has eight states, it is also frequently known as modulus-8 or mod-8 counters. Similarly, a counter with four flip-flops is called mod-16 counters. The modulus of a counter is the total number of its different states, through which it can pass in order to conclude its counting cycle.

Alternative Explanation

For further explanation, a ripple binary counter comprising four JK flip-flops have been illustrated. It has been constructed by means of cascading four flip-flops. Every flip-flop depicted in figure “a” is in its toggle position (that’s every flip-flop’s output has been made clock input for the next flip-flop) and JK input of every flip-flop is high or 1. Of the four binary outputs (A, B, C and D) A output is the smallest bit or LSB (Least Significant Bit), whereas D output is the largest bit or MSB (Most Significant Bit). Remember that clock pulses, which are desired to be counted, are applied on clock input of the first flip-flop i.e. FF1. With the help of this counter, we can count from binary 0000 to binary 1111 (or from 0 to 15 decimal numbers). As this counter counts from binary 0000 to binary 1111 and consists on 16 different output states, therefore it is also known as a 16-mod counter.

Figure 8.2-Mod-16 counter (a). logic diagram (b). waveform diagram

In order to understand the mechanism of this counter, it is assumed that every flip-flop toggles (or changes its state) when a negative clock pulse edge is provided on its clock input. In the beginning, assume that the counter is reset. In such a situation, normal output of all flip-flops are zero. i.e.

DCBA = 0 0 0 0

When first clock pulse is received on the clock input of flip-flop 1 (i.e. FF1), it toggles on negative clock edge (i.e. changes its state and sets). Other flip-flops do not toggle, because they get negative edge from the preceding flip-flops. Thus, as a result of operation of first flip-flop, LSB flip-flop A sets (i.e. becomes 1). Thus, counters’ output state will be as below;

DCBA = 0 0 0 1

It shows that one input pulse has taken place, as can be seen via a truth table shown in figure 8.3. It has been kept in mind that when value of first flop-flop (FF1) returns back from 1 to 0, at that time 2nd flip-flop (FF2) toggles by means of receiving a negative edge. Similarly, when state of the 2nd flip-flop returns from 1 to 0, 3rd flip-flop (FF3) receives a negative edge, as a result of which it tends to toggle. And when state of 3rd flip-flop turns out to be 0 from 1, the fourth flip-flop (FF4), toggles. In other words, whenever a flip-flop resets (that’s a zero state emerges on it), next flip-flop tends to toggle. This has been illustrated via a waveform or timing diagram in figure 8.2 (b).

Figure 8.3-Counting sequence for a 4-bit electronic counter

| BINARY COUNTING | DECIMAL COUNTING | |||

| D | C | B | A | |

| 8s | 4s | 2s | 1s | |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 2 |

| 0 | 0 | 1 | 1 | 3 |

| 0 | 1 | 0 | 0 | 4 |

| 0 | 1 | 0 | 1 | 5 |

| 0 | 1 | 1 | 0 | 6 |

| 0 | 1 | 1 | 1 | 7 |

| 1 | 0 | 0 | 0 | 8 |

| 1 | 0 | 0 | 1 | 9 |

| 1 | 0 | 1 | 0 | 10 |

| 1 | 0 | 1 | 1 | 11 |

| 1 | 1 | 0 | 0 | 12 |

| 1 | 1 | 0 | 1 | 13 |

| 1 | 1 | 1 | 0 | 14 |

| 1 | 1 | 1 | 1 | 15 |

When the 2nd clock pulse strikes, FF1 toggles on negative edge (i.e. changes its state) and it resets. As such, FF1 output turns 0. As FF1 output is connected with FF2 clock input, in such a situation FF2 toggles and gets set (i.e. 1). Now if this new state of output is pondered upon, it is as follows;

DCBA = 0 0 1 0

This output value is an equivalent binary number of decimal 2, which signifies that so far two pulses have occurred. When 3rd clock pulse strikes, FF1 flip-flop resets again and its output becomes binary 1 from binary 0. In such a situation, binary number stored in counter is as follows;

DCBA = 0 0 1 1

This binary number is equal to decimal number 3 (as has been illustrated in the truth table). It means that three pulses have been received on the counter’s input.

When fourth clock pulse strikes, FF1 flip-flop resets, thus its output becomes binary 0 (which was previously binary 1). This binary “0” output of FF1 is received on FF2 clock’s input, due to which its state changes (i.e. FF2 flip-flop also resets and its output also turns out to be binary 0 from binary 1). FF2 output is received on FF3. As such, FF3 flip-flop, which was previously reset (i.e. its output was binary 0) now changes its state and becomes set (i.e. its output becomes binary 1). Under such a scenario, following number is stored in counter;

DCBA = 0 1 0 0

This binary number on counter’s output is equivalent to decimal number 4, as has been demonstrated via truth table. Therefore, following binary output is received as 5th clock pulse strikes;

DCBA = 0 1 0 1

The following output is received as the 6th clock pulse strikes;

DCBA = 0 1 1 0

The following output is received as the 7th clock pulse strikes;

DCBA = 0 1 1 1

When 8th clock pulse strikes, FF1 tends to reset. FF1 flip -flop’s output is received on FF2 flip-flop. As a result, it sets as well (though it was set prior to the arrival of this pulse). FF2 flip-flop output is received on FF3. As a result, this flip-flop also changes its state and resets from set state. FF# flip-flops output is transmitted on FF4. FF4 flip-flop changes its state on the negative edge of 8th clock pulse (i.e. it toggles) and tends to set from reset. Thus, following binary number is obtained on counters’ output.

DCBA = 1 0 0 0

This binary number 1 0 0 0 is equivalent to decimal number 8. As has been illustrated in the truth table. Following output is received on striking of the 9th clock pulse;

DCBA = 1 0 0 1

On the striking of 10th clock pulse, following binary output is received;

DCBA = 1 0 1 0

This operation goes on continuously, until on the 15th clock pulse in this 4-bit counter, maximum capacity binary number 1111 (which is equal to decimal number 15) is stored. As such, when a next clock pulse strikes after this, existing states of all flip-flops change on its negative edge. Therefore, all flip-flops, which were previously set, now tend to be reset (i.e. when FF1 flip-flop is reset, FF2 flip-flop also resets due to it. When FF2 flip-flop resets, FF3 flip-flop also resets because of it. When FF3 flip-flop is reset, it provides output on FF4 and resultantly, FF4 also resets it). Thus, as consequence of all flip-flops being reset, following output is obtained on counter;

DCBA = 0 0 0 0

After this, on receiving the next clock pulse, this counting cycle re-starts according to afore-mentioned mechanism or complete cycle repeats itself. As this counter counts from decimal 0 to decimal 15, therefore it is also known as an up counter.

The afore-mentioned complete mechanism can also be explained by means of waveforms as shown in figure (b). These waveforms reflect counting till binary 1010 (i.e. decimal 10). The top most of these waveforms is clock input, which is a series of clock pulses received from clock at specific time intervals, which has to be counted. Beneath clock waveform, waveforms of all flip-flops (FF1, FF2, FF3 and FF4) have been depicted, which explain flip-flops’ changing states owing to the clock pulses. In the lowest line of all these waveforms, counter’s binary count has been displayed. If vertical lines in this figure are closely evaluated, we come to know that clock (CLK) just triggers FF1 flip-flop. FF1 flip-flop triggers FF2, FF2 triggers FF3 and FF3 flip-flop triggers FF4. As one flip-flop affects other flip-flop, therefore some time is consumed during the triggering operation of all flip-flops. For example, if we concentrate at point on clock pulse 8, it becomes clear that clock triggers flip-flop FF1, as a result of which, its value becomes binary 0. As a result of the influence of flip-flop FF1, flip-flop FF2 also toggles and comes from binary 1 to binary 0. Then flip -flop FF2 provides its output to FF3 and toggles it, as a result of which, FF3 flip-flop also comes on binary 0 from binary 1. However, as soon as flip-flop FF3 output Q becomes binary 0, FF4 flip-flop triggers, therefore as a result of toggle or change in the state of FF4, its output becomes binary 1 from binary 0. If propagation delay time of every flip-flop is 10ns, individual propagation delay time of all flip-flops in a ripple counter is summed up together.

As such, 40 nano seconds time is consumed on passing of an input signal from first flip-flop to the final flip-flop for changing its state. Therefore, as a result of a high propagation delay time, ripple counter speed is low which is a biggest drawback of this type of counter. Remember that it is possible to manufacture a ripple counter of any binary value or capacity by means of adding flip-flops, as illustrated by the logic diagram of a ripple counter. For instance, if 8 flip-flops are mounted on a logic diagram, then an 8-bit flip-flop counter and if 12 flip-flops are inserted, then a 12-bit ripple counter will be constructed.

Afore-mentioned counters are being referred to through different names such as ripple counter, mod-16 counters, 4-bit counter or asynchronous counter. All these names, explain some certain operation of a counter e.g. ripple and asynchronous means that all flip-flops of this counter do not trigger at a time. Mod-16 signifies that this type of counter has 16 states, which it adopts turn by turn. While 4-bit means that there are four binary places on the output of this counter i.e. it produces 4-bit binary numbers on its output.

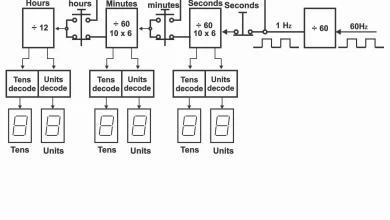

Frequency Dividing Operation of Ripple Counter

This point can be cleared from the waveforms as shown in figure 8.2 (b), that every flip-flop divides its clock frequency by 2 (i.e. output frequency of every flip-flop is one-half or ½ of its input frequency). Therefore, a ripple binary counter can also be used as a frequency divider. As every flip-flop tends to divide a clock frequency by 2, thus if there are “n” flip-flops, they will divide clock frequency by 2n.

The waveforms of FF1 flip-flop‘s output as shown in the figure (b) indicates that its frequency is half comparative to the clock’s input frequency. FF2 flip-flop’s output frequency is half of FF1 flip-flop frequency or ¼ of clock pulses frequency. FF3 flip-flop output frequency is half (½) of FF2 flip-flop output frequency, ¼ as compared to FF1 flip-flop and 1/8 with respect to clock frequency. Likewise, FF4 frequency is 1/16 of the clock frequency. For example, if clock pulses frequency is 100 KHZ, it becomes half on the output of first flip-flop (i.e. 100/2 = 50 KHZ). On the output of 2nd flip-flop, it becomes ¼ (i.e. 100/4 = 25KHZ). On 3rd flip-flop’s output, it becomes 1/8 (i.e. 100/8 = 12.5KHZ) and on fourth’s flip-flop’s output, this frequency becomes 1/16 i.e. 100/16 = 6.25KHZ. Thus,

1 Flip-flop divides the input frequency by 2

2 Flip-flop divides the input frequency by 4

3 Flip-flop divides the input frequency by 8

4 Flip-flop divides the input frequency by 16

N flip-flop divides the input frequency by n2

Previous Topic: Different Types of Shift Registers In Digital Electronics

Next Topic: Synchronous Counter in Digital Electronics with circuit Diagram

For electronics and programming-related projects visit my YouTube channel.

Discover more from Electronic Clinic

Subscribe to get the latest posts sent to your email.